丒僉儍僾僠儍帪

儕僙僢僩乮忋婰僽儘僢僋偵彂偒朰傟偨乯偡傞偲偙偺儌乕僪偵側傞丅

僨乕僞偼堦斒揑側俁慄幃僔儕傾儖揮憲偝傟偰偄傞偺偱丄偙傟傪僨乕僞僶僗僐儞僩儘乕儖懁CPLD偱僷儔儗儖偵栠偡偲偲傕偵丄SRAM偺彂偒崬傒僋儘僢僋傪嶌傞丅傾僪儗僗僶僗僐儞僩儘乕儖CPLD偼嵍婰僋儘僢僋偱儊儌儕彂偒崬傒傪峴偆偺偲扨側傞傾僪儗僗僇僂儞僞偱偁傞丅

傾僪儗僗偑僆乕僶乕僼儘乕偡傞偲LED傪摂偡丅

Visor壒尮傪嶌偭偨偺偩偑摦嶌拞偵掆巭偡傞栤戣偑偁傝丄偙偺壒尮僠僢僾偵揮憲偟偰偄傞僨乕僞傪僉儍僾僠儍偟偨偔側偭偰偒偨丅

偙偺嵺巗斕昳傪巚偄愗偭偰攦偍偆偲巚偭偨偺偩偑丄晛媦壙奿懷偺巗斕昳儘僕傾僫偱傕堄奜偵僉儍僾僠儍偱偒傞梕検偼彮側偄偙偲偑傢偐偭偨丅

崱夞偼僞僀儈儞僌傪夝愅偡傞傛傝偼僨乕僞偺僉儍僾僠儍傪偟偨偐偭偨偩偗側偺偱丄娙扨偵嶌傟偦偆偩丅

丒僽儘僢僋恾

丒僉儍僾僠儍帪

儕僙僢僩乮忋婰僽儘僢僋偵彂偒朰傟偨乯偡傞偲偙偺儌乕僪偵側傞丅

僨乕僞偼堦斒揑側俁慄幃僔儕傾儖揮憲偝傟偰偄傞偺偱丄偙傟傪僨乕僞僶僗僐儞僩儘乕儖懁CPLD偱僷儔儗儖偵栠偡偲偲傕偵丄SRAM偺彂偒崬傒僋儘僢僋傪嶌傞丅傾僪儗僗僶僗僐儞僩儘乕儖CPLD偼嵍婰僋儘僢僋偱儊儌儕彂偒崬傒傪峴偆偺偲扨側傞傾僪儗僗僇僂儞僞偱偁傞丅

傾僪儗僗偑僆乕僶乕僼儘乕偡傞偲LED傪摂偡丅

丒儕乕僩僶僢僋帪

俹俠偱僞乕儈僫儖僜僼僩傪忋偘偰丄儕僞乕儞傪扏偔偲偙偺儌乕僪偵側傞丅

撉傒崬傒傾僪儗僗偼PIC儅僀僐儞偐傜傾僪儗僗僶僗僐儞僩儘乕儖CPLD偵僔儕傾儖揮憲偡傞丅

僨乕僞偼僨乕僞僶僗僐儞僩儘乕儖CPLD偐傜PIC傊僨乕僞傪僔儕傾儖揮憲偡傞丅

PIC偲CPLD偺捠怣偑僔儕傾儖側偺偼丄扨偵PIC偺俬俷偑懌傜側偄偐傜丅

CPLD偑俀屄偵側偭偰偄傞偺傕侾屄偩偲IO偑懌傜側偄偐傜偱偡丅

PIC偱僞乕儈僫儖僜僼僩偱撉傔傞傛偆僨乕僞傪儕僥儔儖曄姺偡傞丅

偁偲偼儗儀儖曄姺偟偰俹俠傊俼俽亅俀俁俀俠憲怣偡傞丅

丒晹昳挷払

CPLD偼庒徏偱擖庤丅仐俉侽侽墌偔偄傜偄偩偭偨偐丠

SRAM丄PIC儅僀僐儞丄俼俽俀俁俀俠僩儔儞僔乕僶偼廐寧偱偡丅

俼俽俀俁俀俠僩儔儞僔乕僶偼俽俹俀俁俁偲偄偆傗偮偱僠儍乕僕億儞僾僐儞僨儞僒撪憼偱偡丅崅偄偺偑擄揰丅

偦偺懠僷乕僣偼僨僢僪僗僩僢僋敔偐傜庢傝弌偟偰偄傑偡丅

慡晹偱亸俁俲掱搙偱偡丅

丒夞楬恾

夞楬恾偼偁傝傑偣傫丅

懍峌惢嶌儌乕僪帪偼夞楬恾傪彂偐側偄偺偱偡丅

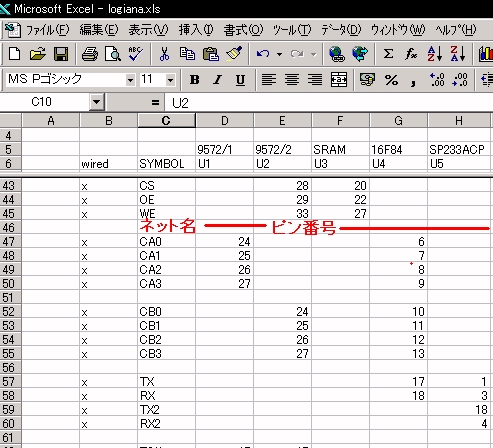

僽儘僢僋恾偐傜擖弌椡慄偺僱僢僩柤傪寛傔丄俬俠偺僺儞斣崋偲偲傕偵僄僋僙儖偵嶌昞偟傑偡丅

婎斅偵晹昳傪幚憰偟丄揹尮攝慄屻丄僄僋僙儖偲偵傜傔偭偙偟偰怣崋儚僀儎傪憱傜偣傑偡丅

埲慜偙偺嶌嬈偡傜徣棯偟偨偲偙傠戝嬯愴偟偨偨傔丄寢壥揑偵偙傟偑嵟懍偺傛偆偱偡丅

偙傫側姶偠偱偡

丒婎斅偺恾

懍峌儌乕僪側偺偱丄嶌傝偼峳偄偱偡丅

SRAM偼昞柺幚憰側偺偱丄僒儞僴儎僩偺曄姺婎斅傪偐傑偟傑偡丅

傕偪傠傫枹巊梡偺僺儞偼僼儘乕僥傿儞僌傎偭偨傜偐偟偱偡偑丄倀倀俿慄偼僾儖僟僂儞偟偰偄傑偡丅

壗傜曐岇夞楬側偳偼嵦梡偟偰偄傑偣傫丅夡傟偨傜偦傟傑偱偱偡丅

丒僜僼僩

俀屄偺CPLD偼VHDL偱婰弎偟偰偄傑偡丅

PIC儅僀僐儞偼傾僙儞僽儔婰弎偱偡丅媣偟傇傝偵傾僙儞僽儔傪巊偭偨偺偱僯乕儌僯僢僋昞庱偭堷偒偱偡丅

偄偄壛尭偵嶌惉偟偰偍傝傑偡偺偱丄偲偰傕岞奐偱偒傞儗儀儖偱偼偁傝傑偣傫丅

偳偺傛偆偵偄偄壛尭偐偲尵偄傑偡偲丄偨偲偊偽僉儍僾僠儍偱偒傞梕検偑俁俀俲俛

亅俀僶僀僩偱偁傝愭摢僶僀僩

偲廔抂僶僀僩偼柍岠乮僑儈僨乕僞乯偱偡丅儖乕僾偺愭抂丒抂枛娗棟側偳偼偄偄壛尭偦偺傕偺偱偡丅

弌椡椺丄扨偵SRAM偺撪梕傪悅傟棳偡偩偗偱偡丅

|

0000:00,31,00,04,39,00,02,39,00,0a,35,00,02,00,43,54,

0010:00,68,64,00,00,00,00,00,06,00,00,00,00,00,01,00,

0020:00,18,00,43,54,38,01,04,32,00,01,00,72,6b,00,00,

0030:00,00,1e,4a,00,00,ff,00,51,03,00,0d,14,00,36,31,

0040:00,c1,30,00,00,c2,00,01,00,00,c3,21,00,00,c9,00,

0050:00,00,00,b1,07,00,7f,00,00,b2,07,00,7f,00,00,b3,

0060:07,00,7f,00,00,b9,07,00,7f,24,00,c0,49,00,00,b0,

|

丒崱屻

偙傟偼栶棫偪傑偟偨丅Visor壒尮偺掆巭栤戣偼曅偯偄偨偺偱丄崱偺偲偙傠弌斣偼側偔側傝傑偟偨丅

崱搙嶌傞偲偒偼旕懍峌儌乕僪偱愝寁偟SDRAM側偳傪巊偄挿儘儞僌儊儌儕偵偟偨偄偲偙傠偱偡丅