32K/44K/48KのVCXOをそれぞれロックするようにコイルを調整する。また、ロック時のVCXO制御電圧が1/2Vccになるようにする。

|

オシロがない場合は、PLLのLPF出力(C24)をテスターで測定し、1/2Vccにする。高インピーダンスのテスターで測定すること。

CDプレーヤしか無い場合は44KのVCXOしか調整できません。DATかBSチューナをゲットするか、低周波発信器等で正確なサンプリング周波数を発生させてPLLの基準入力側につっこんでください。

VCXOの測定

32KHz用VCXOの偏差測定 (0ppm=12.288MHz/V control=2.5V)

|

44KHz用VCXOの偏差測定 (0ppm=16.934MHz/V control=2.5V)

|

48KHz用VCXOの偏差測定 (0ppm=18.432MHz/V control=2.5V)

|

やはりバリキャップを0Vからスイングしたため、低電圧領域で直線性が悪化している。

しかし、設計目標であるプラマイ1000ppmと大きくかけ離れていない。PLLでは周波数変位の直線性はあまり考慮しなくてもよいから、一応合格点だと思う。さらに精度を向上させるためにはバリキャップにバイアスを与え、さらに実験を重ねて水晶の周波数を決定する必要がある。

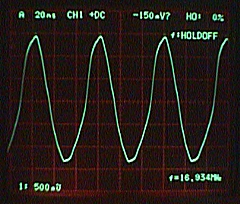

発振波形 (左:バッファFETドレイン側/右:発振トランジスタベース側)

|

|

出力波形の尖頭部が若干汚いが、これはオシロのアースポイントの問題だと思われる。オシロのアースポイントが発振トランジスタのエミッタ側であるため、ベース波形はかなり綺麗である。(但し、ベースはハイZなので、これは参考までだが)

VCXOコイルのダンプ抵抗を当初は33Kで設計したが、コイルのQがまだ高いようで、起動時に変な周波数になることがまれにあったため、15K程度に下げたところ安定した。あまり変えると発振周波数に影響するためこの程度で止めたが、新規設計を起こす場合は10Kかそれ以下のほうが良いと思われる。もちろんその場合は実験が必要である。

測定器:

波形&周波数測定: IWATSU SS-7821

(#オシロにカウンタが入っているのは非常に便利だということが、改めてわかった)