調整が必要なVCXOのコイルは基板作成前に水晶とともに試験しておく。

すべてのDIP ICには丸ピンのICソケットを使用。

デジタルフィルタの出力語長選択ピン、ディザ選択ピンはヘッダ端子とジャンパソケットによるスイッチとした。

入力セレクタ周りのカップリングの6.8uFは積層セラミックを使用。(秋月で入手)

VCXOの電源周りにはタンタルコンデンサを使用。

PLLのLPFにはフィルムコンを使用。

マイクロインダクタは秋月に@10円で売っているやつを使用。容量はあまり気にしていない。

レギュレータは背面がモールドされており、絶縁の必要がないもの(秋月に売っている)を使用する。

PLL IC(TA5081AP)、VCXOのバッファ(2SK241)も秋月に売っている。

トスリンクモジュールは千石電商、若松通商に売っている。(ただし千石のほうが安価であるが、売り切れが多いようだった。)

CS8412は若松通商で入手。SM5842は共立電子で入手。パルストランスも共立電子で入手できた。

コネクタ類はヒロセのもので、千石電商で購入。

その他の部品は何処にでもあると思う。

組立は背の低いものから行うなど定石に従う。

レギュレータ放熱のために、シリコングリスを塗布してGNDパターンに接触させる。

気を付けるのは、基板表面のGNDパターンの”逃げ”で、GND以外のピンと接触していないことを確かめながら取り付ける。

ICソケットの場合は、差し込んで十分押さえつけ、テスターで不用意なショートが無いことを確認してから半田付けする。

リードフォームした部品の場合でもフォーミング部分の曲げがGNDに接触していないか気を付ける。

不安な場合はカッター等でGNDパターンを削る。

#パターンのバグがあった。SM5842のミュートがイネーブルになっていた。表面のGNDとショートする。

#プロトタイプではこのバグはなかったのだが。

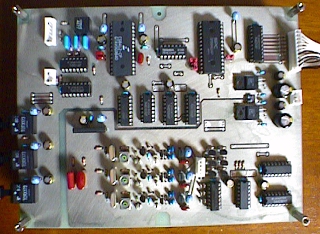

完成したインタフェース基板

|

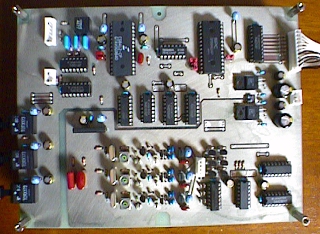

VCXOのアップ(左下から44.1KHz用、48KHz用、32KHz用)

|

本当はこの部分にシールドケースを被せた方が良いのだろう。